# BAT32G179 datasheet

ARM® Cortex®-M0+ based, ultra low power consumption 32-bit microcontroller

Built-in 512K byte Flash, rich simulation function, timer and various communication interfaces

V1.0.3

Please be reminded about following CMS's policies on intellectual property

<sup>\*</sup> Cmsemicon Limited(denoted as 'our company' for later use) has already applied for relative patents and entitled legal rights. Any patents related to CMS's MCU or other producrts is not authorized to use. Any individual, organization or company which infringes our company's interlectual property rights will be forbidden and stopped by our company through any legal actions, and our company will claim the lost and required for compensation of any damage to the company.

<sup>\*</sup> The name of Cmsemicon Limited and logo are both trademarks of our company.

<sup>\*</sup> Our company preserve the rights to further elaborate on the improvements about products function, reliability and design in this manual. However, our company is not responsible for any usage about this manual. The applications and their purposes in this manual are just for clarification, our company does not guarantee that these applications are feasible without further improvements and changes, and our company does not recommend any usage of the products in areas where people's safety is endangered during accident. Our company's products are not authorized to be used for life-saving or life support devices and systems. Our company has the right to change or improve the product without any notification, for latest news, please visit our website: www.mcu.com.cn

#### **Features**

# Ultra-low power consumption operating environment:

- Power supply voltage range:1.8V to 5.5V

- > Temperature range: -40°C to 105°C

- Low power consumption mode: sleep mode, deep sleep mode

- Operating power consumption: 120uA/MHz@64MHz

- Power consumption in deep sleep mode:1.5uA

- Deep sleep mode +32.768K+RTC: 1.9uA

#### Core:

- > ARM®32-bitCortex®-M0+ CPU

- Working frequency: 32KHz~64MHz

#### Memory:

- 512KB Flash memory, with program and data storage shared

- 20KB dedicated data Flash memory

- 64KB SRAM memory with parity check

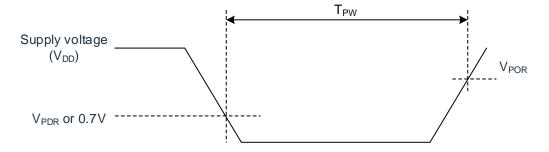

#### Power and reset management:

- > Built-in power-on reset (POR) circuit

- Built-in voltage detection (LVD) circuit (threshold voltage can be set)

#### Clock management:

- Built-in high-speed vibrator, accuracy (±1%). Can provide 1MHz~64MHz system clock and peripheral module operation clock

- Built-in 15KHz low-speed oscillator

- ➤ Built-in 1 PLL

- > Support 1MHz~20MHz external crystal oscillator

- Support 32.768KHz external crystal oscillator, which can be used to calibrate internal high-speed oscillator

#### • Multiplier/divider module:

- Multiplier: Support single cycle 32bit multiplication operation

- Divider: Support 32bit signed integer division operation, only 8 CPU clock cycles to complete an operation

#### Enhanced DMA controller:

- Interrupt trigger start

- Transmission mode is selectable (normal transmission mode, repeated transmission mode, block transmission mode and chain transmission mode)

- The transmission source/destination area is optional for the full address space range

#### Linkage controller:

- The event signals can be linked together to realize the linkage of peripheral functions.

- ➤ 15 types of event input, 10 types of event trigger.

#### Abundant analog peripheral:

- 12-bit precision ADC converter, conversion rate 1.42Msps, 28 external analog channels, internal optional PGA output as conversion channel, with temperature sensor, support single-channel conversion mode and 2, 3, 4 channel scan conversion mode Conversion range: 0 to positive reference voltage

- 8-bit precision D/A converter, 2-channel analog output, real-time output function, output voltage range 0~VDD

- Comparator (CMP), built-in two-channel comparator with hysteresis, optional input source, reference voltage can be external reference voltage or internal reference voltage

- Programmable gain amplifier (PGA), built-in twochannel PGA, can set 4/8/10/12/14/16/32 times gain, with external GND pin (can be used as differential mode)

#### Input/output port:

- Number of I/O port: 59-93

- Can switch between N-channel open drain, TTL input buffer and internal pull-up and pull-down

- > Built-in button interrupt detection function

- Built-in clock output/buzzer output control circuit

#### Serial two-wire debugger (SWD)

#### Abundant timer:

- 16-bit timer: 17 channels (With PWM function and motor dedicated PWM function)

- 15-bit interval timer: 1

- Real-time clock (RTC): 1 (with perpetual calendar, alarm clock function, and supports a wide range of clock correction)

- Watchdog timer (WWDT): 1

- SysTick timer

#### Abundant and flexible interface:

- 4-channel serial communication unit: each channel can be freely configured as a 1-channel standard UART, 2-channel SPI or 2-channel simple I<sup>2</sup>C

- > Standard SPI: 2 channels (Support 8bit and 16bit)

- > Standard I<sup>2</sup>C: 2 channels

- CAN:3 channel

- > LCD BUS interface: support 8080, 6800 interface

#### security function:

- Comply with relevant standards of IEC/UL 60730

- Abnormal storage space access error

- Support RAM parity check

- > Support hardware CRC check

- Support important SFR protection to prevent misoperation

- > 128-bit unique ID number

Flash secondary protection in debug mode (level1: only the entire flash area can be erased, not read or write; level2: the emulator connection is invalid, and the flash operation is not possible)

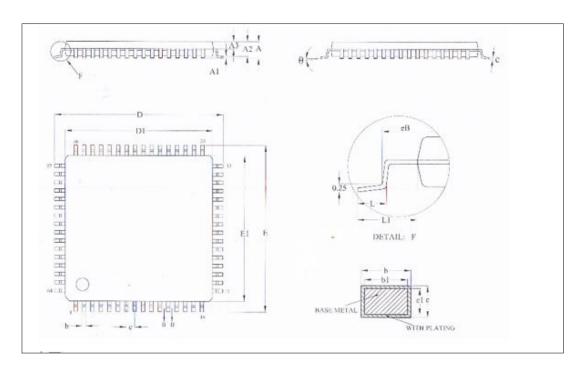

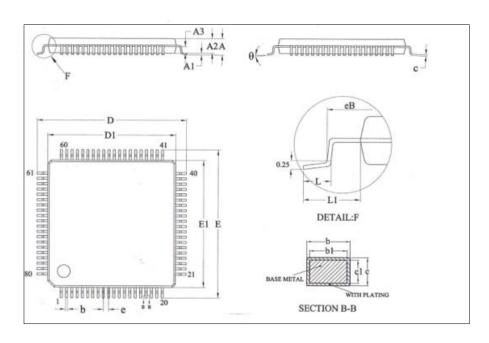

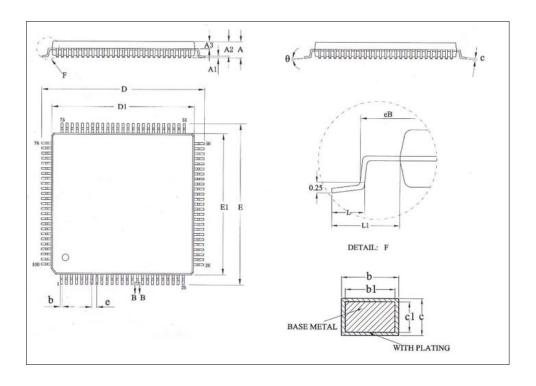

#### • Encapsulation:

Support multiple encapsulation of 64Pin, 80Pin and 100Pin

# 1 Overview

### 1.1 Introduction

Ultra-low power consumption BAT32G179 uses high-performance 32-bit RISC core of ARM®Cortex®-M0+, can work up to 64 MHz, and adopts high-speed embedded flash memory (SRAM max. 64KB, program/data flash memory max. 512KB). This product integrates multiple standard interfaces of I2C, SPI, UART, LIN and CAN bus Integrated 12bit A/D converter, temperature sensor, 8bitD/A converter, comparator, programmable gain amplifier. Among them, the 12bit A/D converter can collect external sensor signals, reducing system design costs. 8bit D/A converter can be used for audio playback or power control. The temperature sensor integrated in the chip can realize real-time monitoring of the external ambient temperature. The internally integrated comparator of the chip can support both high-speed and low-speed operating modes. In the high-speed mode, it can support the control feedback of the high-speed motor, and in the low-speed mode, it can be used for battery monitoring. Integrate a variety of advanced timer modules, load 1-channel SysTick timer, 17-channel 16bit timer, 1-channel 15bit interval timer, watchdog timer and real-time clock and other functions, and can support general-purpose PWM and motor-specific PWM applications.

BAT32G179 also has excellent low-power performance, supports two low-power modes of sleep and deep sleep, and is designed to be flexible. Its operating power consumption is 120uA/MHz@64MHz, and the power consumption is only 1.5uA in deep sleep mode, which is suitable for battery-powered low-power devices. At the same time, due to the integrated event linkage controller, direct connection between hardware modules can be realized without the intervention of the CPU, which is faster than using interrupt response, while reducing the frequency of CPU activity and prolonging the battery life.

These characteristics make the BAT32G179 microcontroller series can be widely used in various application scenarios, such as automotive body control, motor drive control, household appliances and mobile devices and other high-performance low-power applications.

www.mcu.com.cn 4 / 78 Rev 1.0.3

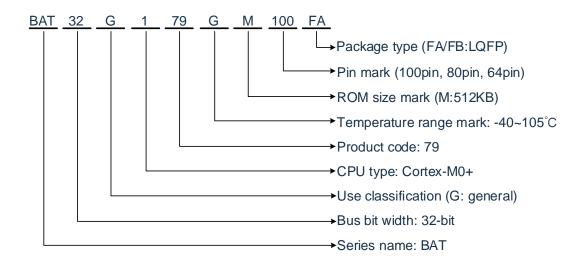

## 1.2 Product Model List

#### List of products of BAT32G179:

| Number of Pin | Encapsulation                | Product model    |  |

|---------------|------------------------------|------------------|--|

| C4 min        | 64-pin plastic package LQFP  | DAT2204700M64ED  |  |

| 64-pin        | (7×7mm, 0.4mm pitch)         | BAT32G179GM64FB  |  |

| 20 =:=        | 80-pin plastic package LQFP  | DAT0004700M00EA  |  |

| 80-pin        | (12×12mm, 0.5mm pitch)       | BAT32G179GM80FA  |  |

| 400 i         | 100-pin plastic package LQFP | DAT0004700M400FA |  |

| 100-pin       | (14×14mm, 0.5mm pitch)       | BAT32G179GM100FA |  |

#### FLASH, SRAM capacity:

|   | Flash  | Special data | SRAM |               | BAT32G179     |                |

|---|--------|--------------|------|---------------|---------------|----------------|

| 1 | memory | Flash memory | SKAW | 64-pin        | 80-pin        | 100-pin        |

|   | 512KB  | 20KB         | 64KB | BAT32G179GM64 | BAT32G179GM80 | BAT32G179GM100 |

www.mcu.com.cn 5 / 78 Rev 1.0.3

#### Product selection table of BAT32G179:

| Part No.             | Kernel | Dominant frequency (MHz) | Min operating voltage (V) | Maxoperating voltage (V) | Code Flash (kB) | SRAM (KB) | Data Flash (KB) | DMA | GPIO | 12bit ADC | 8bit DAC | Comparator CMP | Amplifier PGA | Universal timer (16bit) | Real time clock (RTC) | Watchdog timer (WDT) | Asynchronous serial bus | Synchronous serial bus | IIC bus | LIN bus | CAN bus | Hardware multiplier | Hardware diyider | package     |

|----------------------|--------|--------------------------|---------------------------|--------------------------|-----------------|-----------|-----------------|-----|------|-----------|----------|----------------|---------------|-------------------------|-----------------------|----------------------|-------------------------|------------------------|---------|---------|---------|---------------------|------------------|-------------|

| BAT32G179<br>GM64FB  | M0+    | 64                       | 1.8                       | 5.5                      | 512             | 64        | 20              | 37  | 59   | 16+<br>4  | 2        | 2              | 2             | 17                      | 1                     | 1                    | 3                       | 6                      | 2+6     | 1       | 1       | Υ                   | Υ                | LQFP<br>64  |

| BAT32G179<br>GM80FA  | M0+    | 64                       | 1.8                       | 5.5                      | 512             | 64        | 20              | 38  | 75   | 22+<br>4  | 2        | 2              | 2             | 17                      | 1                     | 1                    | 4                       | 1+8                    | 2+8     | 1       | 2       | Υ                   | Υ                | LQFP<br>80  |

| BAT32G179<br>GM100FA | M0+    | 64                       | 1.8                       | 5.5                      | 512             | 64        | 20              | 40  | 93   | 28+<br>4  | 2        | 2              | 2             | 17                      | 1                     | 1                    | 4                       | 2+8                    | 2+8     | 1       | 3       | Υ                   | Υ                | LQFP<br>100 |

www.mcu.com.cn 6 / 78 Rev 1.0.3

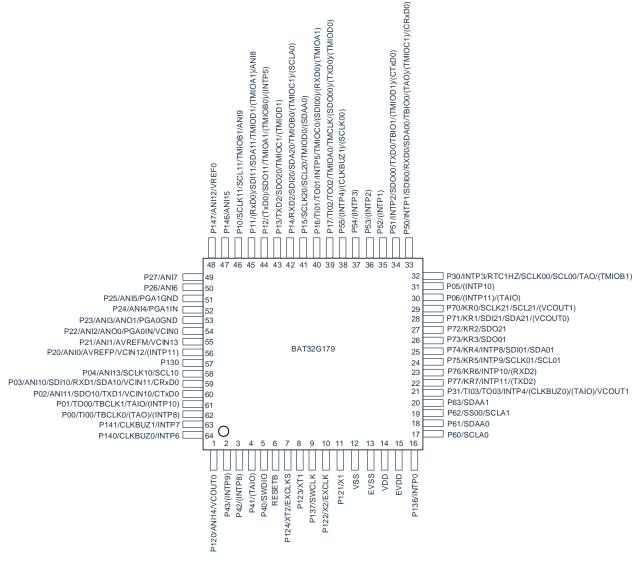

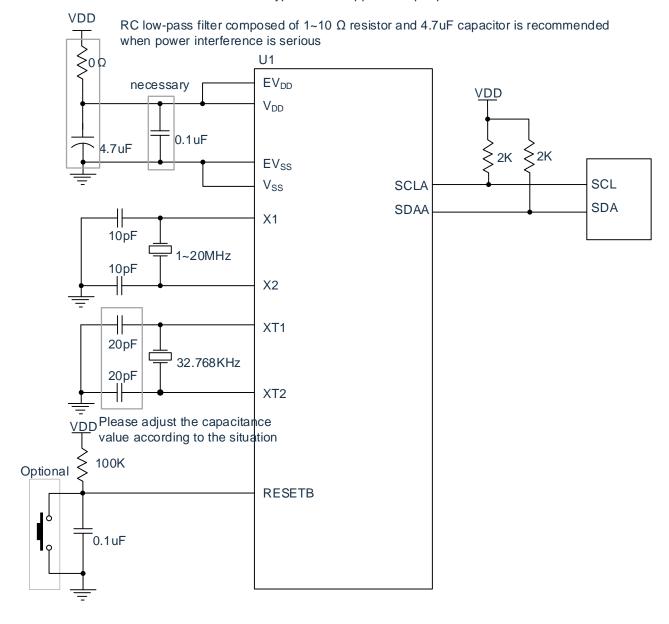

## 1.3 Pin connection diagram (Top View)

## 1.3.1 BAT32G179GM64FB

64-pin plastic package LQFP(7x7mm, 0.4mm pitch)

#### Note:

- 1. EV<sub>SS</sub> pin and V<sub>SS</sub> pin must be at the same potential

- 2. The voltage of V<sub>DD</sub> pin must be equal to the voltage of EV<sub>DD</sub> pin.

- 3. When using the microcontroller for an application where the noise generated inside the microcontroller must be reduced, it is recommended to supply separate powers to the V<sub>DD</sub> and EV<sub>DD</sub> pins and connect the V<sub>SS</sub> and EV<sub>SS</sub> pins to separateground lines.

- 4. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

www.mcu.com.cn 7 / 78 Rev 1.0.3

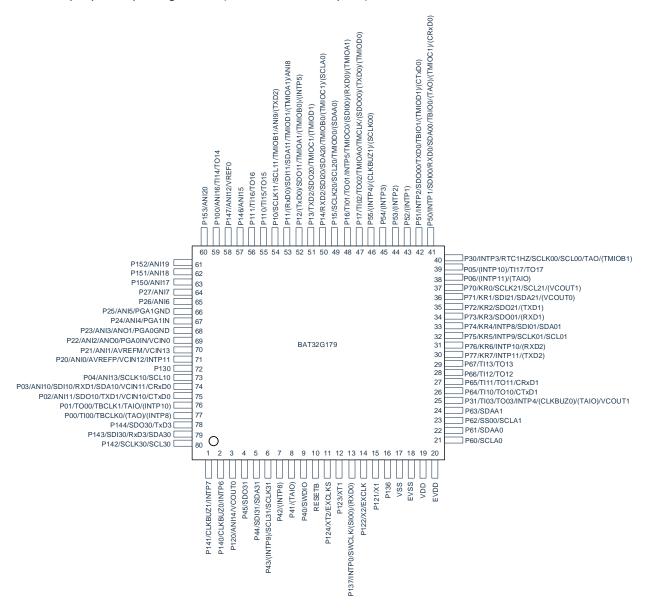

## 1.3.2 BAT32G179GM80FA

• 80-pin plastic package LQFP(12x12mm, 0.5mm pitch)

#### Note:

- 1. EVss pin and Vss pin must be at the same potential

- 2. The voltage of  $V_{DD}$  pin must be equal to the voltage of  $EV_{DD}$  pin.

- 3. When using the microcontroller for an application where the noise generated inside the microcontroller must be reduced, it is recommended to supply separate powers to the V<sub>DD</sub> and EV<sub>DD</sub> pins and connect the V<sub>SS</sub> and EV<sub>SS</sub> pins to separateground lines.

- Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

www.mcu.com.cn 8 / 78 Rev 1.0.3

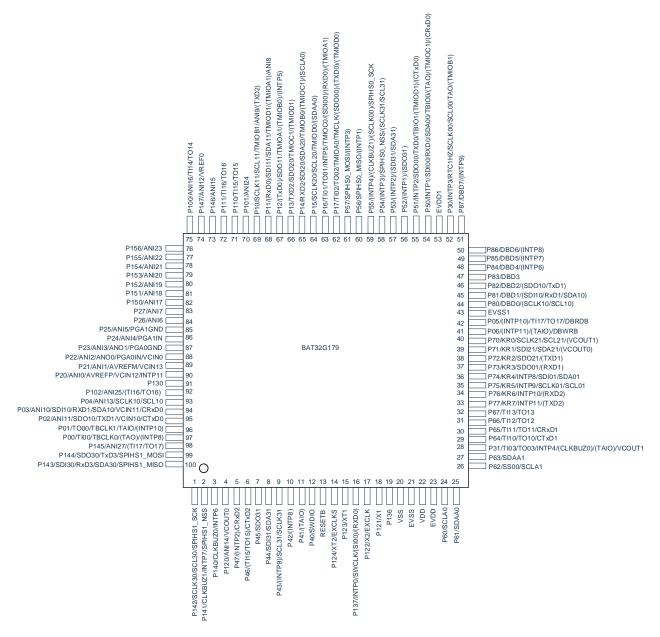

### 1.3.3 BAT32G179GM100FA

• 100-pin plastic package LQFP(14x14mm, 0.5mm pitch)

#### Note:

- 1.  $EV_{SS}$  pin and  $V_{SS}$  pin must be at the same potential

- 2. The voltage of  $V_{DD}$  pin must be equal to the voltage of  $EV_{DD}$  pin.

- 3. When using the microcontroller for an application where the noise generated inside the microcontroller must be reduced, it is recommended to supply separate powers to the V<sub>DD</sub> and EV<sub>DD</sub> pins and connect the V<sub>SS</sub> and EV<sub>SS</sub> pins to separateground lines.

- 4. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

www.mcu.com.cn 9 / 78 Rev 1.0.3

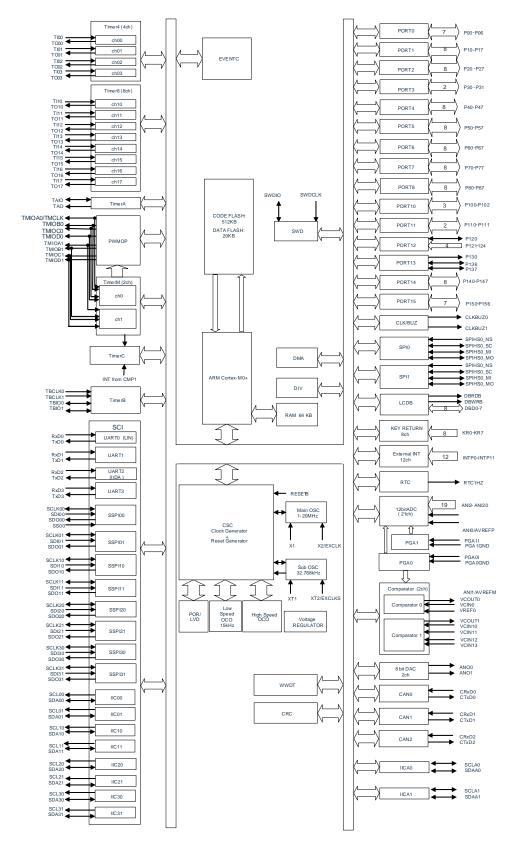

# 2 Block Diagram

Note: The above is for 100-pin product. Some functions of products below 100-pin are not supported.

# 3 Memory Mapping

| FFFF_FFFFH | Keep                                 |

|------------|--------------------------------------|

| E00F_FFFFH | Cortex-M0+ dedicated peripheral area |

| E000_0000H |                                      |

|            | Keep                                 |

| 4005_FFFFH |                                      |

|            |                                      |

|            | Peripheral area                      |

|            |                                      |

|            |                                      |

| 4000_0000H |                                      |

|            | Keep                                 |

| 2000_FFFFH | SRAM (Max 64KB)                      |

| 2000_0000H | ,                                    |

|            | Keep                                 |

| 0050_5FFFH | Data flash 20KB                      |

| 0050_1000H |                                      |

|            | Keep                                 |

| 0007_FFFFH |                                      |

|            | Main flash area (Max 512KB)          |

| 0000_0000H |                                      |

www.mcu.com.cn 11 / 78 Rev 1.0.3

# **4 Pin Function**

# 4.1 Port Function

The relationship between power supply and pins is as follows

| Power/ground | Corresponding Pin                                        |

|--------------|----------------------------------------------------------|

| EVDD/EVSS    | Port pins other than P20~P27, P121~P124, P137 and RESETB |

| VDD/VSS      | • P20~P27, P121~P124, P137 and RESETB                    |

www.mcu.com.cn 12 / 78 Rev 1.0.3

# 4.1.1 64-pin Products

(1/2)

| Function    | I/O  | After Reset     | Alternate Function                                 | Function                                                                                                                                                                                                                                                   |  |  |  |

|-------------|------|-----------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name<br>P00 |      | Release         | TI00/TBCLK0/(TAO)/(INTP8)                          | Port 0.                                                                                                                                                                                                                                                    |  |  |  |

| P01         | -    | Input port      | TO00/TBCLK1/TAIO/(INTP10)                          | 7-bit I/O port. Input/output can be                                                                                                                                                                                                                        |  |  |  |

| P02         | 1    |                 | ANI11/SDO10/TXD1/VCIN10/CTxD0                      | specified in 1-bit units. Use of an on-chip pull-up resistor can be                                                                                                                                                                                        |  |  |  |

| P03         | 1    | Analog function | ANI10/SDI10/RXD1/SDA10/VCIN11/CRxD0                | specified                                                                                                                                                                                                                                                  |  |  |  |

| P04         | I/ O |                 | ANI13/SCLK10/SCL10                                 | by a software setting at input port. Input of P01, P03 and P04 can be set to                                                                                                                                                                               |  |  |  |

| P05         | 1/ 0 |                 | (INTP10)                                           | TTL input buffer.                                                                                                                                                                                                                                          |  |  |  |

| P06         |      | Input port      | (INTP11)/(TAIO)                                    | Output of P00 can be set to N-ch opendrain output (VDD tolerance). P00 and P02 to P04 can be set to analog input                                                                                                                                           |  |  |  |

| P10         |      | Analog          | SCLK11/SCL11/TMIOB1/ANI9                           | Port 1.                                                                                                                                                                                                                                                    |  |  |  |

| P11         |      | function        | (RxD0)/SDI11/SDA11/TMIOD1/(TMIOA1)/ANI8            | 8-bit I/O port.<br>Input/output can be specified in 1-bit                                                                                                                                                                                                  |  |  |  |

| P12         |      |                 | (TxD0)/SDO11/TMIOA1/(TMIOB0)/(INTP5)               | units.                                                                                                                                                                                                                                                     |  |  |  |

| P13         |      |                 | TXD2/SDO20/TMIOC1/(TMIOD1)                         | Use of an on-chip pull-up resistor can be specified                                                                                                                                                                                                        |  |  |  |

| P14         | I/ O | Input port      | RXD2/SDI20/SDA20/TMIOB0/(TMIOC1)/(SCL A0)          | by a software setting at input port. Input of P10 and P14 to P17 can be set                                                                                                                                                                                |  |  |  |

| P15         | 1/ 0 |                 | SCLK20/SCL20/TMIOD0/(SDAA0)                        | to TTL                                                                                                                                                                                                                                                     |  |  |  |

| P16         |      |                 | TI01/TO01/INTP5/TMIOC0/(SDI00)/(RXD0)<br>/(TMIOA1) | input buffer.<br>Output of P10, P11, P13 to P15, and P17                                                                                                                                                                                                   |  |  |  |

| P17         |      |                 | TI02/TO02/TMIOA0/TMCLK/(SDO00)<br>/(TXD0)/(TMIOD0) | can be set to N-ch open-drain output (V <sub>DD</sub> tolerance). P10 to P11 can be set to analog input.                                                                                                                                                   |  |  |  |

| P20         |      |                 | ANIO/AVREFP/VCIN12/(INTP11)                        | . To to dail to cot to alliancy input                                                                                                                                                                                                                      |  |  |  |

| P21         | 1    |                 | ANI1/AVREFM/VCIN13                                 |                                                                                                                                                                                                                                                            |  |  |  |

| P22         | 1    |                 | ANI2/ANO0/PGA0IN/VCIN0                             | Port 2.                                                                                                                                                                                                                                                    |  |  |  |

| P23         | 1/ 0 | Analog          | ANI3/ANO1/PGA0GND                                  | 8-bit I/O port.                                                                                                                                                                                                                                            |  |  |  |

| P24         | I/ O | function        | ANI4/PGA1IN                                        | Input/output can be specified in 1-bit units.                                                                                                                                                                                                              |  |  |  |

| P25         |      |                 | ANI5/PGA1GND                                       | Can be set to analog input.                                                                                                                                                                                                                                |  |  |  |

| P26         |      |                 | ANI6                                               |                                                                                                                                                                                                                                                            |  |  |  |

| P27         |      |                 | ANI7                                               |                                                                                                                                                                                                                                                            |  |  |  |

| P30         |      |                 | INTP3/RTC1HZ/SCLK00/SCL00/TAO<br>/(TMIOB1)         | Port 3.<br>2-bit I/O port.                                                                                                                                                                                                                                 |  |  |  |

| P31         | I/ O | Input port      | TI03/TO03/INTP4/(CLKBUZ0)/(TAIO)<br>/VCOUT1        | Input/output can be specified in 1-bit units.  Use of an on-chip pull-up resistor can be specified by a software setting at input port.  Input of P30 can be set to TTL input buffer.  Output of P30 can be set to N-ch Open-drain output (VDD tolerance). |  |  |  |

(2/2)

| Function<br>Name | I/O  | After Reset<br>Release | Alternate Function                                   | (2/2)<br>Function                                                                                         |

|------------------|------|------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| P40              |      | Neicase                | SWDIO                                                | Port 4.                                                                                                   |

| P41              |      |                        | (TAIO)                                               | 4-bit I/O port.                                                                                           |

| P42              | I/ O | Input port             | (INTP8)                                              | Input/output can be specified in 1-bit units.                                                             |

| P43              |      |                        | (INTP9)                                              | Use of an on-chip pull-up resistor can be specified by a software setting at input port.                  |

| P50              |      |                        | INTP1/SDI00/RXD0/SDA00/TBIO0/(TAO)/(TM IOC1)/(CRxD0) | Port 5.<br>6-bit I/O port.                                                                                |

| P51              |      |                        | INTP2/SDO00/TXD0/TBIO1/(TMIOD1)/(CTxD0)              | Input/output can be specified in 1-bit units.                                                             |

| P52              |      |                        | (INTP1)                                              | Use of an on-chip pull-up resistor can be                                                                 |

| P53              | I/O  | Input port             | (INTP2)                                              | specified by a software setting at input                                                                  |

| P54              |      |                        | (INTP3)                                              | port. Input of P50 andP51 can be set to TTL                                                               |

| P55              |      |                        | (INTP4)/(CLKBUZ1)/(SCLK00)                           | input buffer. Output of P50, p51 and P55 can be set to N-ch opendrain output (V <sub>DD</sub> tolerance). |

| P60              |      |                        | SCLA0                                                | Port 6                                                                                                    |

| P61              |      |                        | SDAA0                                                | 4-bit I/O port.<br>Input/output can be specified in 1-bit                                                 |

| P62              | I/O  | Input port             | SS00/SCLA1                                           | units.                                                                                                    |

| P63              |      |                        | SDAA1                                                | Output of P60~ P63 can be set to N-ch opendrain output (6V tolerance).                                    |

| P70              |      |                        | KR0/SCLK21/SCL21/(VCOUT1)                            | Port 7.                                                                                                   |

| P71              |      |                        | KR1/SDI21/SDA21/(VCOUT0)                             | 8-bit I/O port.                                                                                           |

| P72              |      |                        | KR2/SDO21                                            | Input/output can be specified in 1-bit                                                                    |

| P73              |      |                        | KR3/SDO01                                            | units.                                                                                                    |

| P74              | I/O  | Input port             | KR4/INTP8/SDI01/SDA01                                | Use of an on-chip pull-up resistor can be specified by a software setting at input                        |

| P75              |      |                        | KR5/INTP9/SCLK01/SCL01                               | port.                                                                                                     |

| P76              |      |                        | KR6/INTP10/(RxD2)                                    | Output of P71 and P74 can be set to N-                                                                    |

| P77              |      |                        | KR7/INTP11/(TxD2)                                    | ch opendrain output (EVDD tolerance).                                                                     |

| P120             | I/ O | Analog function        | ANI14/VCOUT0                                         | Port 12.                                                                                                  |

| P121             |      | TUTICUOTI              | X1                                                   | 1-bit I/O port and 2-bit input-only port.  For only P120, input/output can be                             |

| P122             |      |                        | X2/EXCLK                                             | specified.                                                                                                |

| P123             |      |                        | XT1                                                  | For only P120, use of an on-chip pull-up                                                                  |

| P124             | I    | Input port             | XT2/EXCLKS                                           | resistor can be specified by a software setting at input port. P120 can be set to analog input.           |

| P130             | 0    | Output port            |                                                      | Port 13.                                                                                                  |

| P136             |      |                        | INTP0                                                | 1-bit I/O port and 2-bit input-only port. P136 and P137 can be designated as                              |

| P137             | I/ O | Input port             | SWCLK                                                | input or output in bit units. The input port can be set by software, using internal pull-up resistors.    |

| P140             |      |                        | CLKBUZ0/INTP6                                        | Port 14.                                                                                                  |

| P141             |      | Input port             | CLKBUZ1/INTP7                                        | 4-bit I/O port.                                                                                           |

| P146             | I/O  |                        | ANI15                                                | Input/output can be specified.  Use of an on-chip pull-up resistor can be                                 |

| P147             |      | Analog<br>function     | ANI12/VREF0                                          | specified by a software setting at input port.                                                            |

|        |   |   |   | P146 and P147 can be set as analog                    |

|--------|---|---|---|-------------------------------------------------------|

|        |   |   |   | input.                                                |

|        |   |   |   | Input-only pin for external reset.                    |

| RESETB | 1 | _ | _ | Connect to V <sub>DD</sub> directly or via a resistor |

|        |   |   |   | when external reset is not used.                      |

#### Note:

- 1. Each pin can be specified as either digital or analog by setting port mode control register x (PMCx) (Can be specified in 1-bit units).

- 2. Description of Alternate function, please refer to "4.2 Port Multiplexing Function".

- 3. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

www.mcu.com.cn 15 / 78 Rev 1.0.3

# 4.1.2 80-pin Products

(1/2)

| Function<br>Name | I/O  | After Reset<br>Release | Alternate Function                          | Function                                                                                                                                                                                                                                                    |                                                                                                |  |

|------------------|------|------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| P00              |      |                        | TI00/TBCLK0/(TAO)/(INTP8)                   | Port 0.                                                                                                                                                                                                                                                     |                                                                                                |  |

| P01              |      | Input port             | TO00/TBCLK1/TAIO/(INTP10)                   | 7-bit I/O port.<br>Input/output can be specified in 1-bit units.                                                                                                                                                                                            |                                                                                                |  |

| P02              |      |                        | ANI11/SDO10/TXD1/VCIN10/CTxD0               | Use of an on-chip pull-up resistor can be                                                                                                                                                                                                                   |                                                                                                |  |

| P03              | I/O  | Analog function        | ANI10/SDI10/RXD1/SDA10/VCIN11/CRxD0         | specified by a software setting at input port.<br>Input of P01, P03 and P04 can be set to TTL                                                                                                                                                               |                                                                                                |  |

| P04              |      | Turiction              | ANI13/SCLK10/SCL10                          | input buffer.                                                                                                                                                                                                                                               |                                                                                                |  |

| P05              |      |                        | (INTP10)/TI17/TO17                          | Output of P00, P02 to P04 can be set to N-ch                                                                                                                                                                                                                |                                                                                                |  |

| P06              |      | Input port             | (INTP11)/(TAIO)                             | open-drain output (EV <sub>DD</sub> tolerance).<br>P02, P03 and P04 can be set to analog input                                                                                                                                                              |                                                                                                |  |

| P10              |      | Analog                 | SCLK11/SCL11/TMIOB1/ANI9/(TXD2)             | , · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                       |                                                                                                |  |

| P11              |      | function               | (RxD0)/SDI11/SDA11/TMIOD1/(TMIOA1)/ANI8     | Port 1.<br>8-bit I/O port.                                                                                                                                                                                                                                  |                                                                                                |  |

| P12              |      |                        | (TxD0)/SDO11/TMIOA1/(TMIOB0)/(INTP5)        | Input/output can be specified in 1-bit units.                                                                                                                                                                                                               |                                                                                                |  |

| P13              |      |                        | TXD2/SDO20/TMIOC1/(TMIOD1)                  | Use of an on-chip pull-up resistor can be                                                                                                                                                                                                                   |                                                                                                |  |

| P14              | I/ O |                        | RXD2/SDI20/SDA20/TMIOB0/(TMIOC1)/(SC LA0)   | specified by a software setting at input port.                                                                                                                                                                                                              |                                                                                                |  |

| P15              |      | Input port             | SCLK20/SCL20/TMIOD0/(SDAA0)                 | Input of P10 and P14 to P17 can be set to TTL input buffer.                                                                                                                                                                                                 |                                                                                                |  |

| P16              |      |                        |                                             | TI01/TO01/INTP5/TMIOC0/(SDI00)/(RXD0)<br>/(TMIOA1)                                                                                                                                                                                                          | Output of P10, P11, P13 to P15, and P17 can be set to N-ch open-drain output (EV <sub>DD</sub> |  |

| P17              |      |                        |                                             |                                                                                                                                                                                                                                                             |                                                                                                |  |

| P20              |      |                        | ANIO/AVREFP/VCIN12/(INTP11)                 |                                                                                                                                                                                                                                                             |                                                                                                |  |

| P21              |      |                        | ANI1/AVREFM/VCIN13                          |                                                                                                                                                                                                                                                             |                                                                                                |  |

| P22              |      |                        | ANI2/ANO0/PGA0IN/VCIN0                      | Port 2.                                                                                                                                                                                                                                                     |                                                                                                |  |

| P23              |      | Analog                 | ANI3/ANO1/PGA0GND                           | 8-bit I/O port.                                                                                                                                                                                                                                             |                                                                                                |  |

| P24              | I/O  | function               | ANI4/PGA1IN                                 | Input/output can be specified in 1-bit units.                                                                                                                                                                                                               |                                                                                                |  |

| P25              |      |                        | ANI5/PGA1GND                                | Can be set to analog input.                                                                                                                                                                                                                                 |                                                                                                |  |

| P26              |      |                        | ANI6                                        |                                                                                                                                                                                                                                                             |                                                                                                |  |

| P27              |      |                        | ANI7                                        |                                                                                                                                                                                                                                                             |                                                                                                |  |

| P30              |      |                        | INTP3/RTC1HZ/SCLK00/SCL00/TAO /(TMIOB1)     | Port 3.<br>2-bit I/O port.                                                                                                                                                                                                                                  |                                                                                                |  |

| P31              | I/ O | Input port             | TI03/TO03/INTP4/(CLKBUZ0)/(TAIO)<br>/VCOUT1 | Input/output can be specified in 1-bit units.  Use of an on-chip pull-up resistor can be specified by a software setting at input port.  Input of P30 can be set to TTL input buffer.  Output of P30 can be set to N-ch Open-drain output (EVDD tolerance). |                                                                                                |  |

(2/2)

| Function | I/O                | After Reset               | Alternate Function                                                                            | (2/2)<br>Function                                                                                                                                      |                                                 |                                                                                          |                   |                           |                                              |

|----------|--------------------|---------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------|-------------------|---------------------------|----------------------------------------------|

| Name     | 1/0                | Release                   |                                                                                               |                                                                                                                                                        |                                                 |                                                                                          |                   |                           |                                              |

| P40      | _                  |                           | SWDIO                                                                                         | Port 4<br>6-bit I/O port.                                                                                                                              |                                                 |                                                                                          |                   |                           |                                              |

| P41      | _                  | Input port                | (TAIO)                                                                                        | Input/output can be specified in 1-bit units.                                                                                                          |                                                 |                                                                                          |                   |                           |                                              |

| P42      | I/ O               |                           | (INTP8)                                                                                       | Use of an on-chip pull-up resistor can be specified by a software setting at input port.                                                               |                                                 |                                                                                          |                   |                           |                                              |

| P43      | 1/ 0               |                           | input port                                                                                    | input port                                                                                                                                             | input port                                      | input port                                                                               | input port        | (INTP9)/SCLK31/SCL31      | Input of P43 and P44 can be set to TTL input |

| P44      |                    |                           |                                                                                               |                                                                                                                                                        |                                                 | SDA31/SDI31                                                                              | buffer.           |                           |                                              |

| P45      |                    |                           | SDO31                                                                                         | Output of P43 and P44 can be set to N-ch Open-drain output (EV <sub>DD</sub> tolerance).                                                               |                                                 |                                                                                          |                   |                           |                                              |

| P50      |                    |                           | INTP1/SDI00/RXD0/SDA00/TBIO0/(TAO) /(TMIOC1)/(CRxD0) INTP2/SDO00/TXD0/TBIO1/(TMIOD1)/(CT xD0) |                                                                                                                                                        |                                                 |                                                                                          | /(TMIOC1)/(CRxD0) | Port 5<br>6-bit I/O port. |                                              |

| P51      |                    |                           |                                                                                               | Input/output can be specified in 1-bit units. Use of an on-chip pull-up resistor can be                                                                |                                                 |                                                                                          |                   |                           |                                              |

| P52      | I/O                | Input port                | (INTP1)                                                                                       | specified by a software setting at input port.                                                                                                         |                                                 |                                                                                          |                   |                           |                                              |

| P53      | 1                  |                           | (INTP2)                                                                                       | Input of P50 and P55 can be set to TTL input                                                                                                           |                                                 |                                                                                          |                   |                           |                                              |

| P54      |                    |                           | (INTP3)                                                                                       | buffer. Output of P50, P51 and P55 can be set to N-                                                                                                    |                                                 |                                                                                          |                   |                           |                                              |

| P55      | 1                  |                           | (INTP4)/(CLKBUZ1)/(SCLK00)                                                                    | ch Open-drain output (EV <sub>DD</sub> tolerance).                                                                                                     |                                                 |                                                                                          |                   |                           |                                              |

| P60      |                    |                           | SCLA0                                                                                         |                                                                                                                                                        |                                                 |                                                                                          |                   |                           |                                              |

| P61      | 1                  |                           | SDAA0                                                                                         |                                                                                                                                                        |                                                 |                                                                                          |                   |                           |                                              |

| P62      | 1                  |                           | SS00/SCLA1                                                                                    | Port 6                                                                                                                                                 |                                                 |                                                                                          |                   |                           |                                              |

| P63      | -                  |                           | SDAA1                                                                                         | 8-bit I/O port.                                                                                                                                        |                                                 |                                                                                          |                   |                           |                                              |

| P64      | I/ O               | Input port                | TI10/TO10/CTxD1                                                                               | Input/output can be specified in 1-bit units.                                                                                                          |                                                 |                                                                                          |                   |                           |                                              |

| P65      |                    |                           | TI11/TO11/CRxD1                                                                               | Output of P60 to P63 can be set to N-ch Open-<br>drain output (6V tolerance).                                                                          |                                                 |                                                                                          |                   |                           |                                              |

| P66      | -                  |                           | TI12/TO12                                                                                     |                                                                                                                                                        |                                                 |                                                                                          |                   |                           |                                              |

| P67      | -                  |                           | TI13/TO13                                                                                     | -                                                                                                                                                      |                                                 |                                                                                          |                   |                           |                                              |

| P70      |                    |                           | KR0/SCLK21/SCL21/(VCOUT1)                                                                     |                                                                                                                                                        |                                                 |                                                                                          |                   |                           |                                              |

| P71      | 1                  |                           |                                                                                               |                                                                                                                                                        |                                                 | KR1/SDI21/SDA21/(VCOUT0)                                                                 | -                 |                           |                                              |

| P72      | 1                  |                           | KR2/SDO21/(TXD1)                                                                              | Port 7.<br>8-bit I/O port.                                                                                                                             |                                                 |                                                                                          |                   |                           |                                              |

| P73      | 1                  |                           | KR3/SD001/(RXD1)                                                                              | Input/output can be specified in 1-bit units.                                                                                                          |                                                 |                                                                                          |                   |                           |                                              |

| P74      | I/O                | Input port                | O Input port                                                                                  | O Input port                                                                                                                                           | O Input port                                    | O Input port                                                                             | Input port        | KR4/INTP8/SDI01/SDA01     | Use of an on-chip pull-up resistor can be    |

| P75      | 1                  |                           |                                                                                               |                                                                                                                                                        | KR5/INTP9/SCLK01/SCL01                          | specified by a software setting at input port.  Output of P71 and P74 can be set to N-ch |                   |                           |                                              |

| P76      | 1                  |                           |                                                                                               | KR6/INTP10/(RxD2)                                                                                                                                      | open-drain output (EV <sub>DD</sub> tolerance). |                                                                                          |                   |                           |                                              |

| P77      | -                  |                           | KR7/INTP11/(TxD2)                                                                             | -                                                                                                                                                      |                                                 |                                                                                          |                   |                           |                                              |

| 1 7 7    |                    |                           | (17/1411 11/(17DZ)                                                                            | Port 10.                                                                                                                                               |                                                 |                                                                                          |                   |                           |                                              |

| P100     | I/ O               | Analog function           | ANI16/TI14/TO14                                                                               | 1-bit I/O port. Input/output can be specified in 1-bit units. Use of an on-chip pull-up resistor can be specified by a software setting at input port. |                                                 |                                                                                          |                   |                           |                                              |

| P110     |                    |                           | TI15/TO15                                                                                     | Port 11.                                                                                                                                               |                                                 |                                                                                          |                   |                           |                                              |

| P111     | I/ O               | Input port                | TI16/TO16                                                                                     | 2-bit I/O port. Input/output can be specified in 1-bit units. Use of an on-chip pull-up resistor can be specified by a software setting at input port. |                                                 |                                                                                          |                   |                           |                                              |

| P120     | I/O                | Analog function           | ANI14/VCOUT0                                                                                  | Port 12.                                                                                                                                               |                                                 |                                                                                          |                   |                           |                                              |

| P121     |                    |                           | X1                                                                                            | 1-bit I/O port and 2-bit input-only port. For only P120, input/output can be specified.                                                                |                                                 |                                                                                          |                   |                           |                                              |

| P122     | 1                  |                           | X2/EXCLK                                                                                      | For only P120, use of an on-chip pull-up                                                                                                               |                                                 |                                                                                          |                   |                           |                                              |

| P123     |                    | Input port                | XT1                                                                                           | resistor can be specified by a software setting at input port. P120 can be set to                                                                      |                                                 |                                                                                          |                   |                           |                                              |

| P124     | 1                  |                           | XT2/EXCLKS                                                                                    | analog input.                                                                                                                                          |                                                 |                                                                                          |                   |                           |                                              |

| P130     | 0                  | Output port               |                                                                                               | Port 13.                                                                                                                                               |                                                 |                                                                                          |                   |                           |                                              |

| P136     |                    |                           | _                                                                                             | 1-bit I/O port and 2-bit input-only port.                                                                                                              |                                                 |                                                                                          |                   |                           |                                              |

| P137     | I/ O Input port IN | INTP0/SWCLK/(SI00)/(RXD0) | P136 and P137 can be designated as input or output in bit units. The input port can be set by |                                                                                                                                                        |                                                 |                                                                                          |                   |                           |                                              |

|          | l                  | 1                         |                                                                                               | 1                                                                                                                                                      |                                                 |                                                                                          |                   |                           |                                              |

|        |     |            |                  | software, using internal pull-up resistors.                                                                                |

|--------|-----|------------|------------------|----------------------------------------------------------------------------------------------------------------------------|

| P140   |     |            | CLKBUZ0/INTP6    | Port 14.                                                                                                                   |

| P141   |     |            | CLKBUZ1/INTP7    | 7-bit I/O port. Input/output can be specified in 1-bit units.                                                              |

| P142   |     | Input port | SCLK30/SCL30     | Use of an on-chip pull-up resistor can be                                                                                  |

| P143   | I/O |            | SDI30/RxD3/SDA30 | specified by a software setting at input port. Input of P142 and P143 can be set to TTL                                    |

| P144   |     |            | SDO30/TxD3       | input buffer.                                                                                                              |

| P146   |     | Analog     | ANI15            | Output of P142, P143, and P144 can be set to                                                                               |

| P147   |     | function   | ANI12/VREF0      | N-ch open-drain output (EV <sub>DD</sub> tolerance). P146 and P147 can be set to analog input                              |

| P150   |     |            | ANI17            | Port 15.                                                                                                                   |

| P151   |     | Analog     | ANI18            | 4-bit I/O port. Input/output can be specified in 1-bit units.                                                              |

| P152   | I/O | function   | ANI19            | Use of an on-chip pull-up resistor can be                                                                                  |

| P153   |     |            | ANI20            | specified by a software setting at input port.  Can be set to analog input                                                 |

| RESETB | 1   | _          | _                | Input-only pin for external reset.  Connect to V <sub>DD</sub> directly or via a resistor when external reset is not used. |

#### Note:

- 1. Each pin can be specified as either digital or analog by setting port mode control register x (PMCx) (Can be specified in 1-bit units).

- 2. Description of Alternate function, please refer to "4.2 Port Multiplexing Function".

- 3. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

www.mcu.com.cn 18 / 78 Rev 1.0.3

# 4.1.3 100-pin Products

(1/3)

| Function<br>Name | I/O  | After Reset<br>Release | Alternate Function                                 | Function                                                                                                                      |  |

|------------------|------|------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| P00              | I/ O |                        | TI00/TBCLK0/(TAO)/(INTP8)                          | Port 0.                                                                                                                       |  |

| P01              |      | Input port             | TO00/TBCLK1/TAIO/(INTP10)                          | 7-bit I/O port. Input/output can be specified in 1-bit units.                                                                 |  |

| P02              |      |                        | ANI11/SDO10/TXD1/VCIN10/CTxD0                      | Use of an on-chip pull-up resistor can be                                                                                     |  |

| P03              |      | Analog function        | ANI10/SDI10/RXD1/SDA10/VCIN11/CRxD0                | specified by a software setting at input port.                                                                                |  |

| P04              |      | Turiction              | ANI13/SCLK10/SCL10                                 | Input of P01, P03 and P04 can be set to TTL                                                                                   |  |

| P05              |      | Input port             | (INTP10)/TI17/TO17/DBRDB                           | input buffer.                                                                                                                 |  |

| P06              |      |                        | (INTP11)/(TAIO)/DBWRB                              | Output of P00 can be set to N-ch open-drain output (V <sub>DD</sub> tolerance). P00 and P02 to P04 can be set to analog input |  |

| P10              | I/ O | Analog                 | SCLK11/SCL11/TMIOB1/ANI9/(TXD2)                    |                                                                                                                               |  |

| P11              |      | function               | (RxD0)/SDI11/SDA11/TMIOD1/(TMIOA1)/ANI8            | Port 1.<br>8-bit I/O port.                                                                                                    |  |

| P12              |      | Input port             | (TxD0)/SDO11/TMIOA1/(TMIOB0)/(INTP5)               | Input/output can be specified in 1-bit units.                                                                                 |  |

| P13              |      |                        | TXD2/SDO20/TMIOC1/(TMIOD1)                         | Use of an on-chip pull-up resistor can be specified                                                                           |  |

| P14              |      |                        | RXD2/SDI20/SDA20/TMIOB0/(TMIOC1)/(SC LA0)          | by a software setting at input port. Input of P10 and P14 to P17 can be set to TTL                                            |  |

| P15              |      |                        | SCLK20/SCL20/TMIOD0/(SDAA0)                        | input buffer.                                                                                                                 |  |

| P16              |      |                        | TI01/TO01/INTP5/TMIOC0/(SDI00)/(RXD0)              | Output of P10, P11, P13 to P15, and P17 can be                                                                                |  |

| P17              |      |                        | /(TMIOA1)                                          | set to N-ch open-drain output (V <sub>DD</sub> tolerance).                                                                    |  |

| F 17             |      |                        | TI02/TO02/TMIOA0/TMCLK/(SDO00)<br>/(TXD0)/(TMIOD0) | P10 to P11 can be set to analog input.                                                                                        |  |

| P20              | I/ O | Analog function        | ANIO/AVREFP/VCIN12/INTP11                          |                                                                                                                               |  |

| P21              |      | Tunction               | ANI1/AVREFM/VCIN13                                 |                                                                                                                               |  |

| P22              |      |                        | ANI2/ANO0/PGA0IN/VCIN0                             | Port 2.                                                                                                                       |  |

| P23              |      |                        | ANI3/ANO1/PGA0GND                                  | 8-bit I/O port.                                                                                                               |  |

| P24              |      |                        | ANI4/PGA1IN                                        | Input/output can be specified in 1-bit units.                                                                                 |  |